Преимущества дифференциальной пары на MOSFET транзисторах с активной нагрузкой

В данной статье мы обсудим два преимущества использования активной нагрузки: улучшенные условия смещения и преобразование дифференциального сигнала в несимметричный.

Вспомогательная информация

- Схемы на дискретных полупроводниковых компонентах: Дифференциальный усилитель

- Схемы на дискретных полупроводниковых компонентах: Простой операционный усилитель на дискретных элементах

- Полевые транзисторы с изолированным затвором (MOSFET)

- Базовая схема источника стабилизированного тока на MOSFET транзисторах

- Базовая схема дифференциальной пары на MOSFET транзисторах

Предыдущая статья

Улучшенное смещение

В предыдущей статье была представлена «проблема с резистором стока»: для достижения более высокого коэффициента усиления нам нужен больший резистор стока, но большее сопротивление стока означает более низкое постоянное напряжение смещения в выходном узле.

Это проблема, поскольку выходное напряжение также является напряжением стока MOSFET транзистора, а более низкое напряжение стока соответствует более высокому риску выталкивания полевого транзистора из состояния насыщения в триодную (линейную) область. Мы предположили, что источник тока мог бы решить эту проблему, обеспечивая высокий коэффициент усиления, не оказывая негативного влияния на условия смещения.

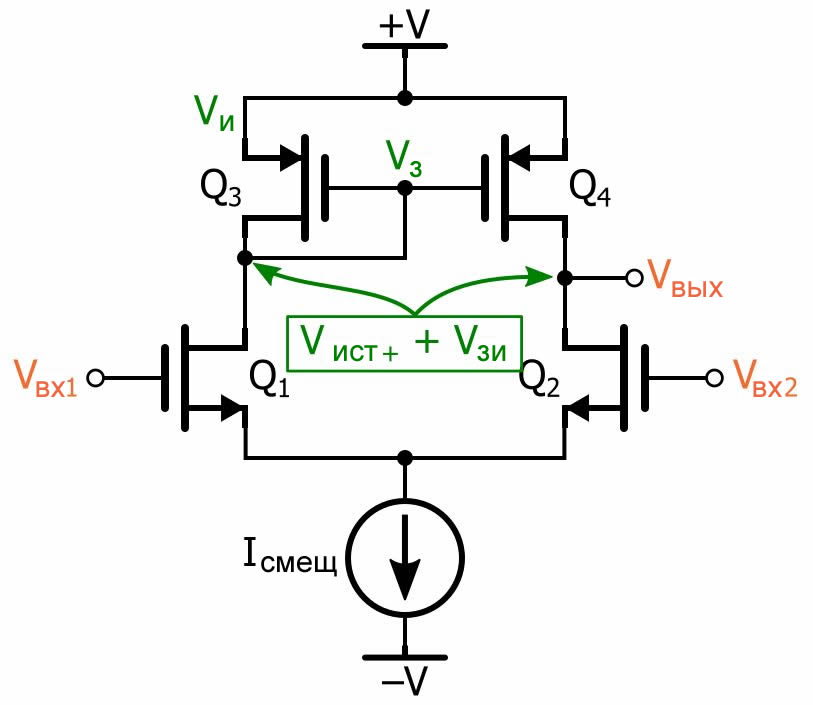

Следующая диаграмма дает представление об улучшенной ситуации со смещением, связанной с использованием токового зеркала вместо резисторов стока.

Мы еще не обсуждали сопротивление активной нагрузки из токового зеркала малым сигналам, поэтому сейчас вы просто должны поверить мне, когда я скажу, что оно достаточно высокое. Но, как видно из принципиальной схемы, это большое сопротивление малым сигналам не относится к условиям смещения: напряжение смещения в выходном узле определяется тем, какое напряжение затвор-исток соответствует току стока Q3.

Если учесть, что этот ток стока не особенно велик и пороговое напряжение Q3 составляет, возможно, 0,7 В, мы можем предположить, что величина Vзи будет весьма мала по сравнению с высоким коэффициентом усиления, обусловленным большим сопротивлением токового зеркала малым сигналам.

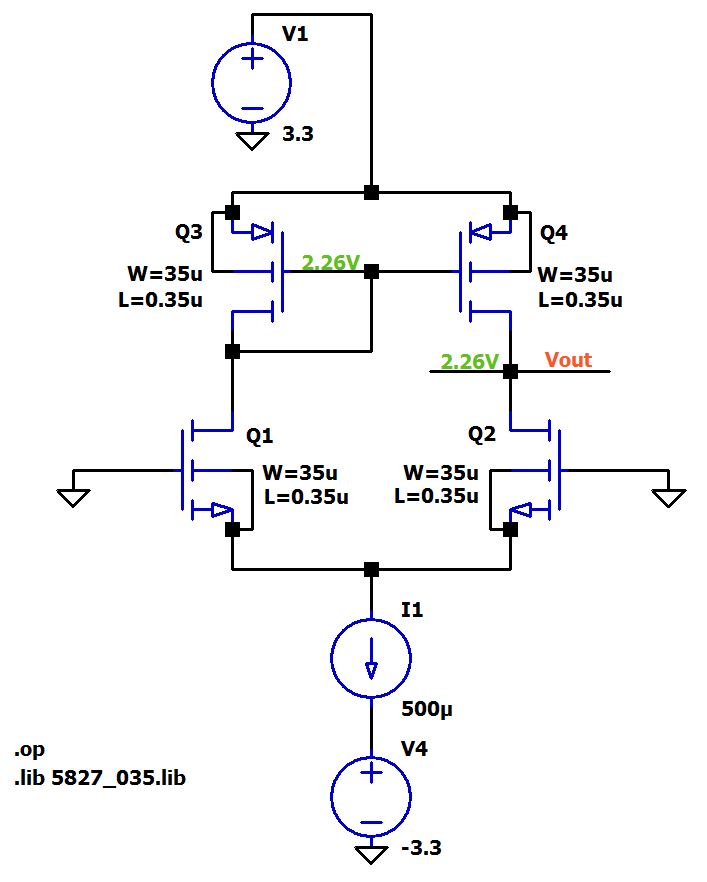

Давайте подтвердим это предположение с помощью моделирования. Ниже показана схема LTspice с отмеченным напряжением смещения:

Это моделирование демонстрирует, что большое сопротивление токового зеркала малым сигналам (и, следовательно, высокий коэффициент усиления) не требует большого падения постоянного напряжения. С помощью этой конкретной схемы Q3 может генерировать ток, равный Iсмещ/2 (то есть 250 мкА) с напряжением затвор-исток всего –1,04 В, что приводит к напряжению смещения выходного узла (3,3 + Vзи) = 2,26. V.

Пока мы обсуждаем эту тему, я должен отметить, что на напряжение смещения будет влиять отношение ширины канала к длине канала у транзисторов токового зеркала. Напомним, что связь в режиме насыщения между напряжением затвор-исток и током стока (если мы игнорируем модуляцию длины канала) является следующей:

\[I_с=\frac{1}{2}\mu_nC_{ox}\frac{W}{L}(V_{зи}-V_{порог})^2\]

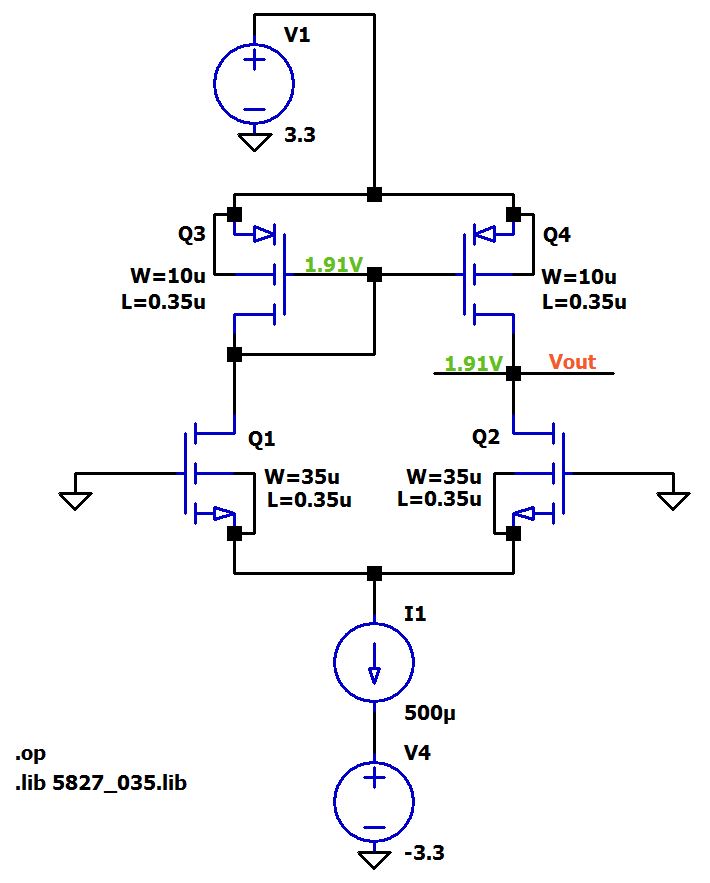

Мы можем видеть, что более низкое отношение ширины канала к его длине заставит полевой транзистор проводить меньший ток стока для того же Vзи. Аналогично, если ток стока поддерживается постоянным и отношение ширины канала к его длине уменьшается, величина Vзи должна будет вырасти. Тогда, теоретически, мы могли бы точно подстраивать напряжение смещения, регулируя у транзисторов токового зеркала отношение ширины канала к его длине. Рассмотрим следующее моделирование:

Диапазон выходных напряжений ограничен положительным напряжением питания и самым низким напряжением, которое позволяет Q2 оставаться в режиме насыщения. Условием насыщения является Vзс ≤ Vпорог, поэтому этот нижний предел равен постоянное напряжение смещения, приложенное к затвору Q2, минус Vпорог вольт. В данной схеме у нас постоянное напряжение смещения 0 В, и Vпорог для NMOS транзисторов ~ 0,5 В, поэтому нижний предел составляет около –0,5 В. Таким образом, уменьшив ширину до 10 мкм, мы сместили напряжение смещения выходного узла ближе к середине допустимого диапазона.

Прежде чем мы продолжим, я должен отметить, что в реальной жизни схема смещения, показанная выше, не практична. Напряжение смещения Vвых имеет очень важное значение: если оно слишком высокое (или слишком низкое), положительный (или отрицательный) размах сигнала на выходе будет ограничен. Смещение, достигнутое в наших моделированиях, является надежным только потому, что Q3 и Q4 идеально согласованы.

Мы можем положиться на технологию производства микросхем в достижении хорошего согласования, но не идеального, и любые несовпадения характеристик этих двух транзисторов приведут к изменениям напряжения смещения Vвых. Таким образом, в реальных реализациях используются специальные схемы смещения, которые не так чувствительны к несовершенствам производства.

Два выхода или один?

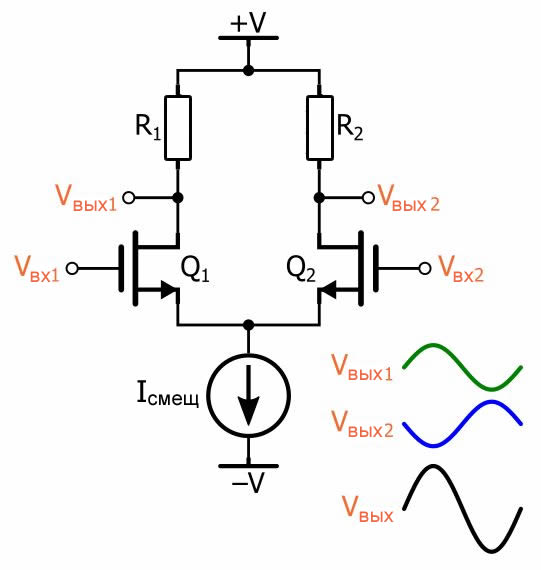

Возможно, вы заметили, что левый Vвых исчез, когда мы переключились с резисторов стока на токовое зеркало. Оказывается, что дополнительное (и, возможно, несколько неожиданное) преимущество активной нагрузки состоит в том, что она преобразует выходной сигнал из дифференциального в несимметричный без потери усиления.

Если вы читали статью «Базовая схема дифференциальной пары на MOSFET транзисторах», вы, возможно, помните, что мы анализировали общий коэффициент усиления разностно, то есть выходной сигнал определялся как Vвых1 - Vвых2. Разность фаз у этих двух сигналов составляет 180°, поэтому амплитуда результирующего выходного сигнала удваивается.

Однако во многих случаях нам не нужны дифференциальные выходные сигналы. Самый простой способ сделать выход несимметричным – просто проигнорировать Vвых1 или Vвых2, но это уменьшит наш коэффициент усиления в 2 раза. Тогда чрезвычайно удобно, что схема с активной нагрузкой выполняет преобразование дифференциального сигнала в несимметричный без уменьшения коэффициента усиления. Давайте взглянем на то, как она выполняет этот подвиг.

Имейте в виду, что это будет анализ для малых сигналов – нас интересует только то, как схема реагирует на небольшие изменения напряжения или тока. Эти небольшие изменения можно рассматривать как отдельный «малый сигнал», который накладывается на сигнал смещения. Я буду использовать строчные буквы для обозначения этих малых сигналов (например, vзи, iс). Не позволяйте этому методу малых сигналов отвлекать вас от того факта, что малые сигналы на самом деле не существуют как отдельные объекты; они просто представляют небольшие изменения в величинах большого сигнала (то есть, смещения по постоянному току). Причина, по которой мы рассматриваем их как отдельные объекты, заключается в том, что анализ для малых сигналов может игнорировать постоянную составляющую сигналов и при этом давать точные результаты.

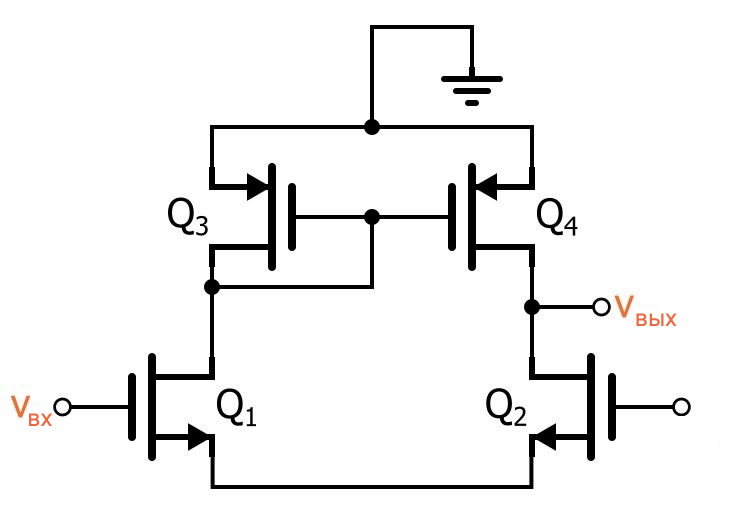

При проведении анализа для малых сигналов мы заменяем источники постоянного тока на разрыв цепи, а источники постоянного напряжения – на короткие замыкания. Таким образом, мы будем использовать следующую принципиальную схему:

Таким образом, если мы прикладываем положительный входной малый сигнал vвх, мы получим ток стока для малого сигнала, проходящий вниз через Q1. Это приводит к выходному напряжению, равному току стока, умноженному на сопротивление стока (будь то реальный резистор стока или сопротивление Q3 для малых сигналов). Пока что нет принципиальной разницы между схемой активной нагрузки и схемой с резистором стока.

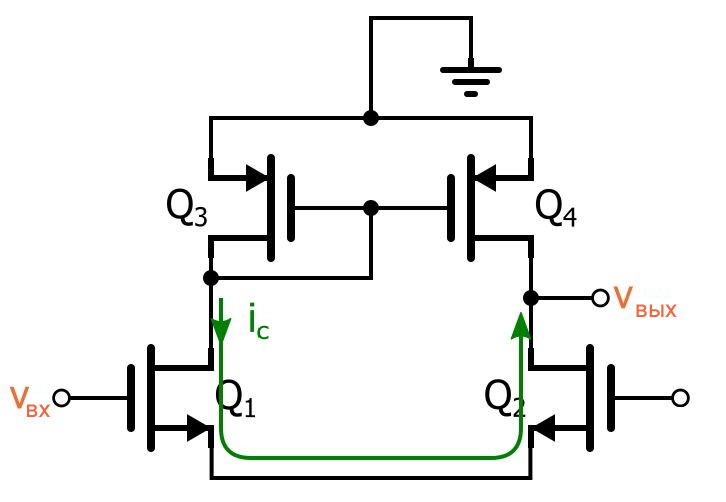

Однако обратите внимание, что этот ток стока будет продолжать течь вдоль нижней части схем и подниматься вверх через Q2:

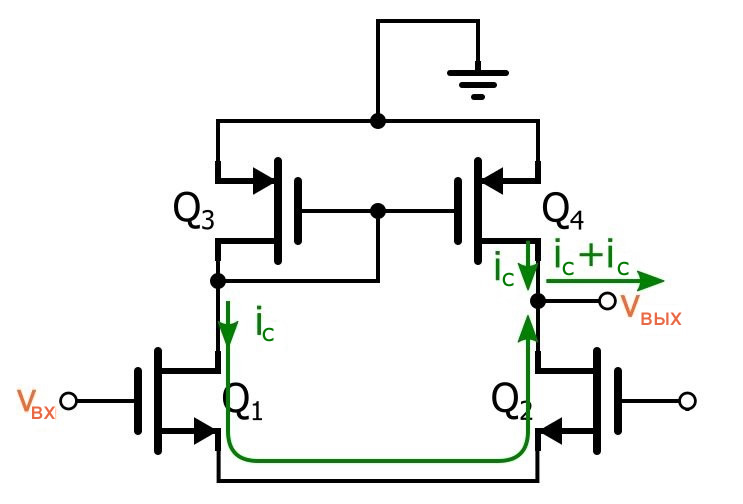

Таким образом, у нас есть iс, направляющийся к выходному узлу. Но давайте не будем забывать об активной нагрузке из токового зеркала – при условии, что два полевых транзистора токового зеркала имеют одинаковое отношение ширины канала к длине, Q4 будет дублировать ток стока Q3 следующим образом:

Таким образом, у нас есть два тока, равные iс, которые встречаются в выходном узле Результирующая величина тока равна iс + iс = 2iс, и это удвоение выходного тока является причиной того, что схема с активной нагрузкой достигает величины полного дифференциального усиления, используя только один выходной сигнал.

Заключение

Я надеюсь, что вы теперь понимаете эти два преимущества активной нагрузки, описанные в этой статье: улучшенное смещение и преобразование дифференциального сигнала в несимметричный. Однако наш интерес к этим преимуществам тесно связан с ожиданием того, что активная нагрузка также может дать нам более высокий коэффициент усиления по сравнению с использованием резистора стока.

В следующей статье мы проанализируем эту схему с точки зрения дифференциального усиления.