Как буферизовать выход операционного усилителя для получения более высокого тока, часть 3

Предыдущие две статьи фокусировались на биполярных транзисторах. В этой статье мы рассмотрим использование для буфера MOSFET транзистора, вместо биполярного транзистора.

Вспомогательная информация

- Введение в операционные усилители

- Аудиоусилитель класса B

- Полевые транзисторы с изолированным затвором (MOSFET)

Биполярный транзистор против полевого MOSFET транзистора: постоянное соперничество

Мне часто хочется, чтобы на этот старый вопрос был получен краткий, однозначный ответ: «Что лучше, биполярный транзистор или полевой MOSFET транзистор?». Но, как вы, наверное, знаете, это всё равно, что спросить: «Что лучше, легковые автомобили или грузовики?». На оба вопроса нет универсального ответа; скорее, подробности каждой конкретной ситуации определяют, какой вариант предпочтительнее. В данной статье мы рассмотрим использование MOSFET транзисторов в конкретном контексте буферизации выхода операционного усилителя для получения более высокого выходного тока, и в процессе мы сможем сформировать общее представление о том, когда MOSFET транзисторы могут быть предпочтительнее биполярных транзисторов, и наоборот.

Краткий обзор

Сначала давайте рассмотрим некоторые знаковые характеристики MOSFET транзисторов.

- Когда полевой транзистор работает в активной области (также называемой насыщением), ток, протекающий через канал MOSFET транзистора, почти полностью контролируется напряжением затвор-исток; в линейной (или триодной) области ток также зависит от напряжения сток-исток.

- MOSFET транзистор начинает проводить ток, когда напряжение затвор-исток превышает пороговое напряжение. Величина тока (в активной области) пропорциональна квадрату напряжения перегрузки (overdrive voltage), которое определяется как напряжение затвор-исток минус пороговое напряжение.

- Затвор MOSFET транзистора изолирован от остальной части устройства, поэтому постоянный ток, протекающий через затвор, практически равен нулю. Я говорю «почти ноль», потому что некоторый ток утечки течет через диэлектрик затвора; для наших целей этот ток утечки незначителен, хотя это и проблематично для чрезвычайно тонких (то есть, менее 2 нм) диэлектриков затвора, используемых в современных интегральных микросхемах.

- Физическая структура затвора MOSFET транзистора приводит к относительно большой емкости – в контексте предмета этой статьи, она может быть, в 5 раз выше, чем входная емкость эквивалентного биполярного транзистора.

NPN прочь, NMOS заходи

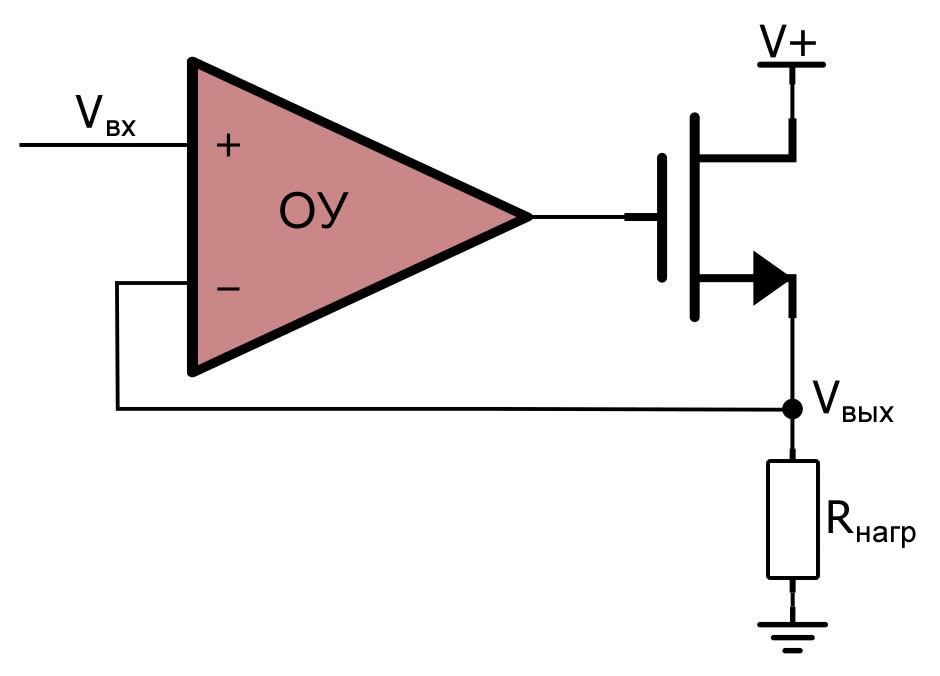

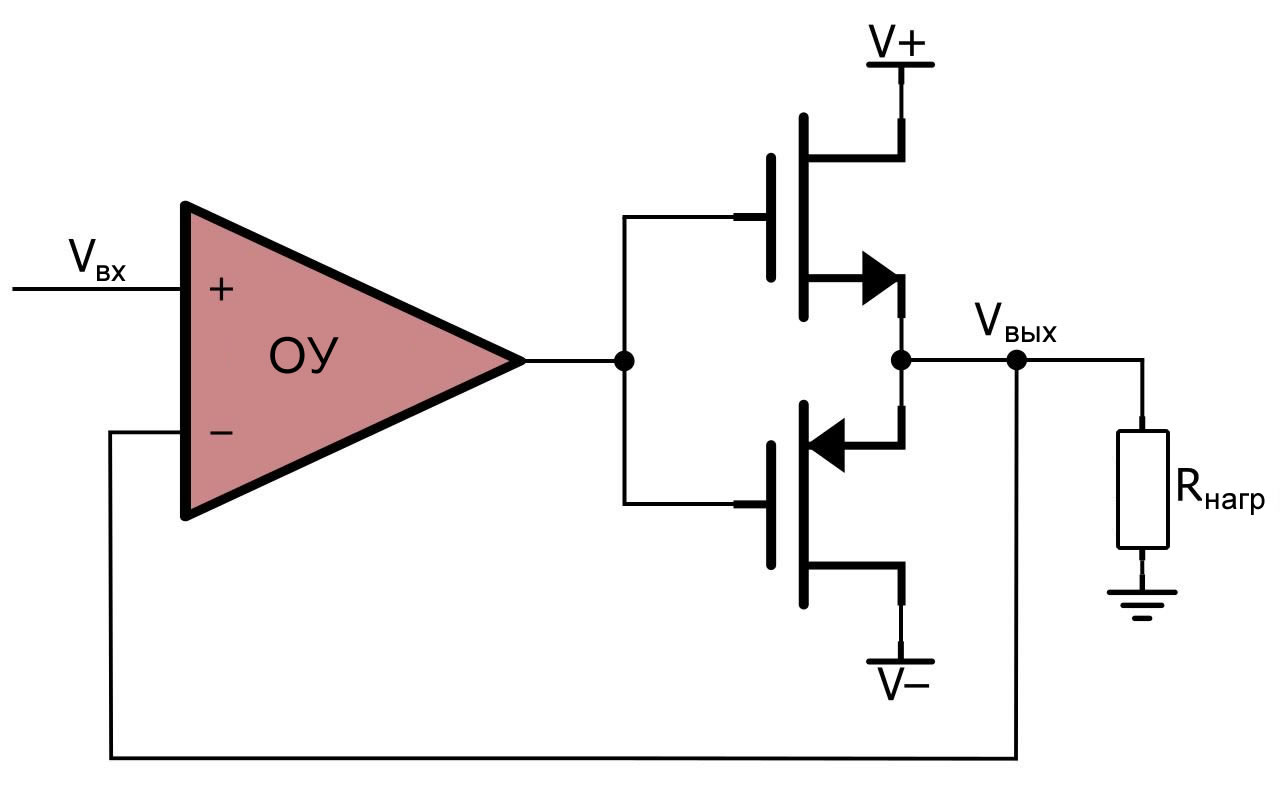

Вот первая схема буферизации с MOSFET транзистором (а именно, NMOS транзистором, MOSFET транзистором с каналом N-типа) вместо биполярного транзистора:

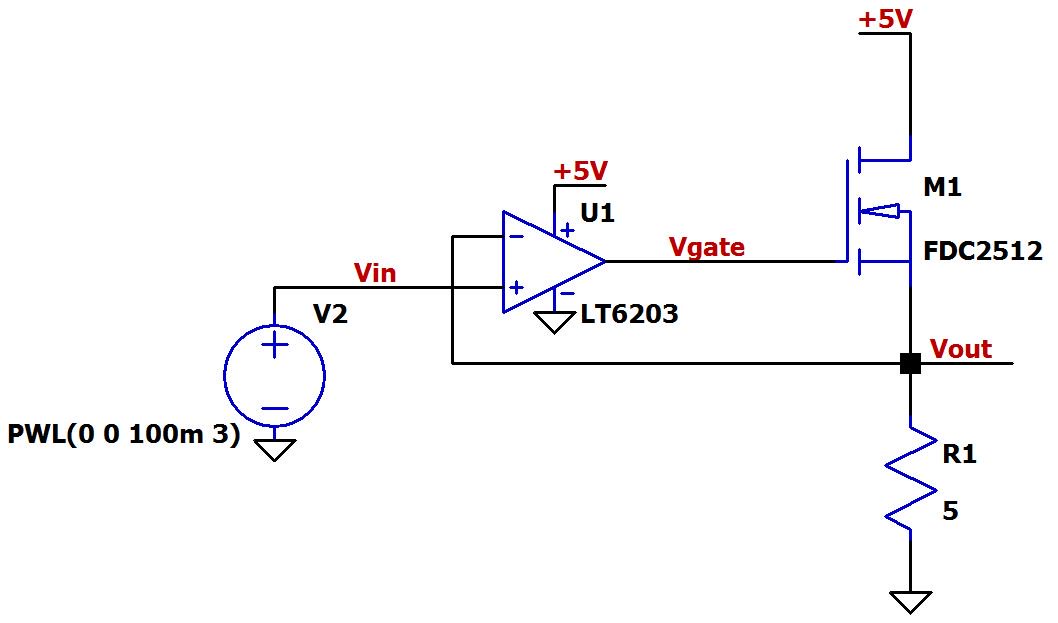

А вот схема LTspice:

Я выбрал модель NMOS транзистора на основе максимального тока стока; я хотел что-то похожее по характеристикам на NPN транзистор 2SCR293P, который мы использовали в первой статье из серии, чтобы сравнение было более релевантным. Максимальный непрерывный ток коллектора 2SCR293P составляет 1 А, а максимальный непрерывный ток стока для FDC2512 – 1,4 А. Эти два компонента также имеют одинаковые пределы рассеивания мощности. Как и ожидалось, имеется значительная разница во входной емкости: у 2SCR293P около 90 пФ; у FDC2512 около 375 пф.

Пороговое напряжение

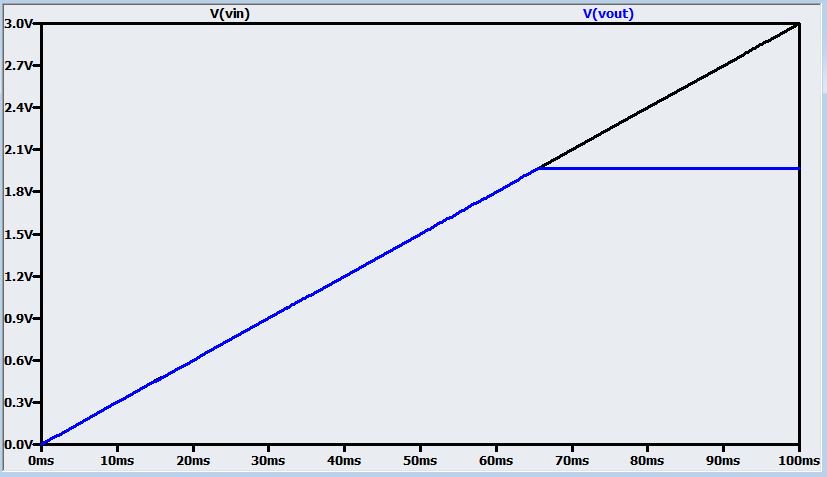

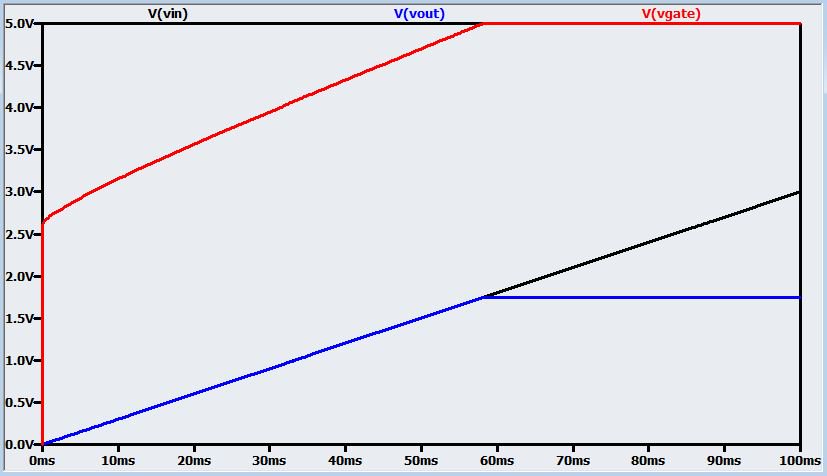

Вот график с входным напряжением VIN и выходным напряжением VOUT схемы.

Проблема очевидна: уровень напряжения нагрузки чуть ниже 2 В, хотя у нас есть 5 В на NMOS транзисторе и операционном усилителе. Следующий график раскрывает причину.

Как можете видеть, напряжение затвора насыщается положительным напряжением с операционного усилителя, когда напряжение нагрузки составляет всего около 2 В. Основная проблема здесь – это пороговое напряжение MOSFET транзистора: полевой транзистор даже не начинает работать, пока напряжение затвор-исток не будет равно 2,6 В. Это означает, что выходное напряжение операционного усилителя всегда будет как минимум на 2,6 В выше, чем напряжение нагрузки, поскольку разность напряжений будет увеличиваться только по мере увеличения тока стока – как показано на предыдущем графике (рисунок 3), когда уровень выходного напряжения выравнивается, напряжение затвор-исток составляет 3 В. Фактически, напряжения, показанные на графике, представляют типовые характеристики FDC2512; согласно спецификации, пороговое напряжение может достигать 4 В!

Это первое моделирование демонстрирует существенный недостаток использования NMOS транзистора в этой схеме: пороговое напряжение намного выше, чем 0,7–0,9 В, требующееся для перехода база-эмиттер NPN транзистора. Конечно, пороговое напряжение варьируется от модели к модели, поэтому вы наверняка могли бы решить эту проблему, выбрав другой полевой транзистор. Быстрый поиск показывает, что NMOS транзисторы, рассчитанные на непрерывный ток стока 1–2 А, могут иметь пороговое напряжение намного ниже 2,6 В. Тем не менее, здесь необходимо соблюдать осторожность, поскольку пороговое напряжение NMOS транзистора склонно быть выше, чем напряжение база-эмиттер 0,7–0,9 В, которое можно ожидать практически от любого NPN-транзистора. Даже пара Дарлингтона (обсуждаемая во второй статье из серии) обеспечит диапазон напряжений нагрузки, равный или больший, чем некоторые MOSFET транзисторы, и составной транзистор Дарлингтона снижает ток базы до уровней, с которыми может справиться практически любой операционный усилитель.

Еще одна деталь, о которой следует помнить: диапазон напряжений нагрузки становится более ограниченным при больших токах нагрузки, поскольку операционный усилитель, чтобы получить более высокий ток стока, должен создавать более высокое напряжение перегрузки. Если мы установим сопротивление нагрузки 2 Ом, вместо 5 Ом, мы получим следующий график:

В этом случае напряжение нагрузки выравнивается на уровне 1,75 В вместо 2 В.

«Прием» и «отдача» тока

Это обсуждение NMOS транзисторов также добавляет PMOS транзистор, который вы бы использовали в качестве «принимающего ток» устройства на выходном каскаде класса B (обсуждается в части 2).

Производительность каскада на NMOS-PMOS транзисторах может быть сопоставима с каскадом на NPN-PNP транзисторах; просто убедитесь, что вы выбираете свои полевые транзисторы тщательно для достаточно низкого порогового напряжения.

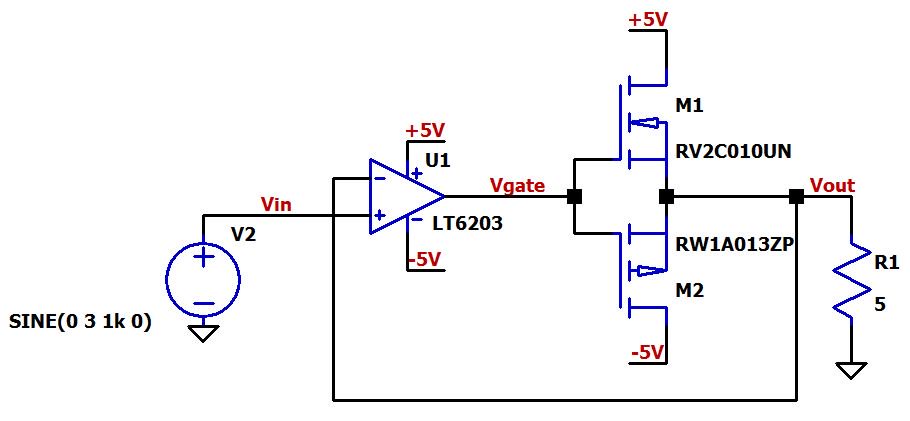

Вот схема LTspice:

У меня были проблемы с поиском подходящих деталей для NMOS и PMOS транзисторов среди вариантов, присутствующих в LTspice по умолчанию, поэтому вместо этого я использую две модели полевых транзисторов с низким пороговым напряжением от ROHM Semiconductor. NMOS – это модель RV2C010UN, а PMOS – это модель RW1A013ZP. Ссылки, прикрепленные к этим моделям, приведут вас к страницам описаний, где вы можете скачать SPICE модели (сразу в разделе «TECHNICAL DOCUMENTS»).

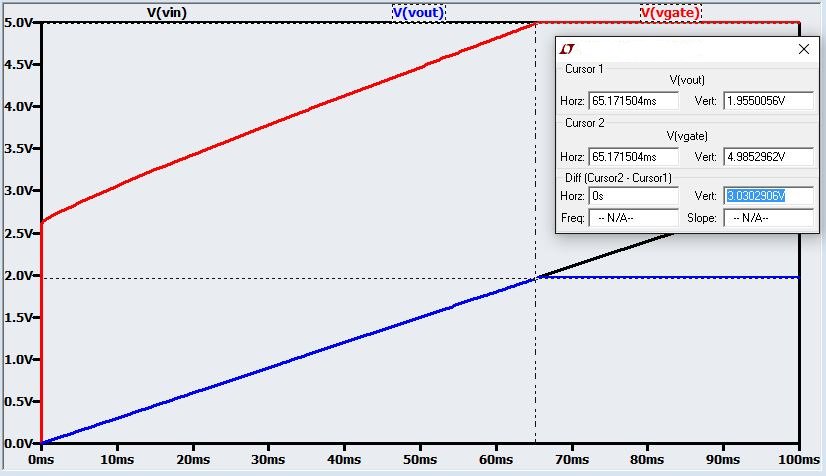

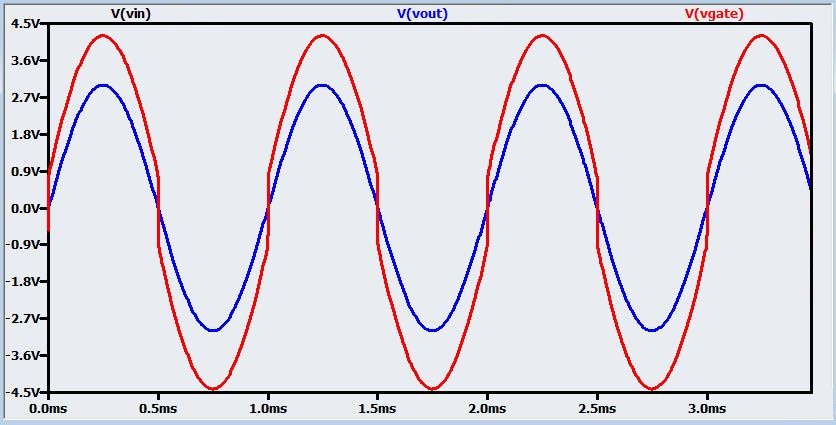

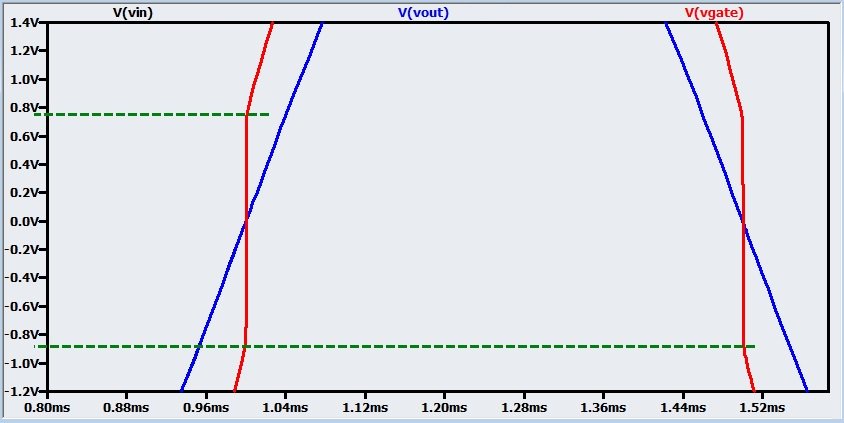

Вот диаграмма с графиками входного напряжения схемы VIN, выходного напряжения схемы VOUT и напряжения на затворах транзисторов VGATE (выходного напряжения операционного усилителя):

График входного напряжения VIN скрыт под графиком выходного напряжения VOUT. Как и в версии на биполярных транзисторах, выходное напряжение операционного усилителя (т. е. VGATE) обходит мертвую зону, в которой оба полевых транзистора находятся в режиме отсечки. Кроме того, этот график отлично подходит для визуализации того, как разница между напряжением на затворах транзисторов, VGATE, и выходным напряжением схемы, VOUT, увеличивается по мере увеличения VOUT (и, следовательно, увеличения тока нагрузки); это отражает основу работы MOSFET транзисторов в активном режиме, а именно, более высокий ток стока требует большего напряжения перегрузки.

Если мы увеличим масштаб, то увидим, что пороговые напряжения у NMOS и PMOS транзисторов составляют около 0,75 В и 0,9 В соответственно. Таким образом, у этих моделей пороговые напряжения не намного выше, чем падения напряжения база-эмиттер биполярных транзисторов.

Заключение

Базовые схемы буферизации тока операционного усилителя могут хорошо работать как с биполярными транзисторами, так и с MOSFET транзисторами. Основным преимуществом MOSFET транзисторов является незначительный выходной ток, требующийся от операционного усилителя, а основная проблема заключается в том, что диапазон выходного напряжения может быть ограничен относительно высокими напряжениями затвор-исток. В следующей статье мы рассмотрим тонкую, но важную проблему, которая может усложнить использование MOSFET транзисторов для буферизации тока операционного усилителя: влияние емкости затвора на стабильность.