EN 302 755. 6.1 FEC кодирование

Данная подсистема должна осуществлять внешнее кодирование (BCH), внутреннее кодирование (LDPC) и битовое перемежение. Входной поток должен состоять из BBFRAME кадров, а выходной — из FECFRAME кадров.

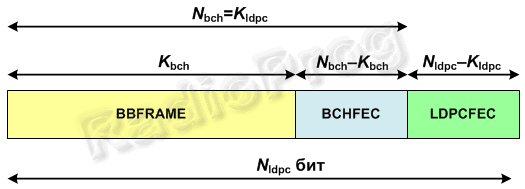

Каждый BBFRAME кадр (Kbch бит) должен быть обработан подсистемой FEC кодирования для формирования FECFRAME кадра (Nldpc бит). Биты проверки на четность (BCHFEC) внешнего систематического BCH кода должны быть добавлены после BBFRAME кадра, а биты проверки на четность (LDPCFEC) внутреннего LDPC кодера должны быть добавлены после поля BCHFEC, как показано на рисунке 12.

(Nldpc = 64 800 бит для стандартного FECFRAME кадра, Nldpc = 16 200 бит для короткого FECFRAME кадра)

В таблице 6(a) приведены параметры кодирования для стандартного FECFRAME кадра (Nldpc = 64 800 бит), а в таблице 6(b) — для короткого FECFRAME кадра (Nldpc = 16 200 бит).

| Скорость LDPC кодирования | Размер блока до BCH кодирования Kbch |

Размер блока после BCH кодирования Nbch Размер блока до LDPC кодиро;вания Kldpc |

Корректирующая способность BCH кода | Nbch—Kbch | Размер блока после LDPC кодирования Nldpc |

|---|---|---|---|---|---|

| 1/2 | 32 208 | 32 400 | 12 | 192 | 64 800 |

| 3/5 | 38 688 | 38 880 | 12 | 192 | 64 800 |

| 2/3 | 43 040 | 43 200 | 10 | 160 | 64 800 |

| 3/4 | 48 408 | 48 600 | 12 | 192 | 64 800 |

| 4/5 | 51 648 | 51 840 | 12 | 192 | 64 800 |

| 5/6 | 53 840 | 54 000 | 10 | 160 | 64 800 |

| Идентификатор скорости LDPC кодирования | Размер блока до BCH кодирования Kbch |

Размер блока после BCH кодирования Nbch Размер блока до LDPC кодирования Kldpc |

Корректирующая способность BCH кода | Nbch—Kbch | Эффективная скорость LDPC кодирования Kldpc/16 200 |

Размер блока после LDPC кодирования Nldpc |

|---|---|---|---|---|---|---|

| 1/4 (смотрите примечание) |

3 072 | 3 240 | 12 | 168 | 1/5 | 16 200 |

| 1/2 | 7 032 | 7 200 | 12 | 168 | 4/9 | 16 200 |

| 3/5 | 9 552 | 9 720 | 12 | 168 | 3/5 | 16 200 |

| 2/3 | 10 632 | 10 800 | 12 | 168 | 2/3 | 16 200 |

| 3/4 | 11 712 | 11 880 | 12 | 168 | 11/15 | 16 200 |

| 4/5 | 12 432 | 12 600 | 12 | 168 | 7/9 | 16 200 |

| 5/6 | 13 152 | 13 320 | 12 | 168 | 37/45 | 16 200 |

|

Данная скорость кодирования используется только для защиты сигнализации L1-pre, но не для защиты данных. |

||||||

Для Nldpc = 64 800, а также для Nldpc = 16 200 скорость LDPC кодирования задается отношением Kldpc/Nldpc. В таблице 6a скорости LDPC кодирования для Nldpc = 64 800 заданы значениями столбца «Скорость LDPC кодирования». В таблице 6b скорости LDPC кодирования для Nldpc = 16 200 заданы значениями столбца «Эффективная скорость LDPC кодирования», т.е. для Nldpc = 16 200 «идентификатор скорости LDPC кодирования» не эквивалентен скорости LDPC кодирования.

Для использования совместно с T2-Lite задан немного другой набор скоростей кодирования — смотрите приложение I.

6.1.1 Внешнее кодирование (BCH)

Исправляющее BCH кодирование (Nbch, Kbch) должно быть применено к каждому BBFRAME кадру для формирования пакета, защищенного от ошибок. Параметры BCH кодирования для Nbch = 64 800 приведены в таблице 6a, а для Nbch = 16 200 — в таблице 6b.

Порождающий полином BCH кодера для исправления t ошибок получается перемножением первых t полиномов в таблице 7a для Nbch = 64 800 или в таблице 7b для Nbch = 16 200.

| g1(x) | 1+x2+x3+x5+x16 |

| g2(x) | 1+x+x4+x5+x6+x8+x16 |

| g3(x) | 1+x2+x3+x4+x5+x7+x8+x9+x10+x11+x16 |

| g4(x) | 1+x2+x4+x6+x9+x11+x12+x14+x16 |

| g5(x) | 1+x+x2+x3+x5+x8+x9+x10+x11+x12+x16 |

| g6(x) | 1+x2+x4+x5+x7+x8+x9+x10+x12+x13+x14+x15+x16 |

| g7(x) | 1+x2+x5+x6+x8+x9+x10+x11+x13+x15+x16 |

| g8(x) | 1+x+x2+x5+x6+x8+x9+x12+x13+x14+x16 |

| g9(x) | 1+x5+x7+x9+x10+x11+x16 |

| g10(x) | 1+x+x2+x5+x7+x8+x10+x12+x13+x14+x16 |

| g11(x) | 1+x2+x3+x5+x9+x11+x12+x13+x16 |

| g12(x) | 1+x+x5+x6+x7+x9+x11+x12+x16 |

| g1(x) | 1+x+x3+x5+x14 |

| g2(x) | 1+x6+x8+x11+x14 |

| g3(x) | 1+x+x2+x6+x9+x10+x14 |

| g4(x) | 1+x4+x7+x8+x10+x12+x14 |

| g5(x) | 1+x2+x4+x6+x8+x9+x11+x13+x14 |

| g6(x) | 1+x3+x7+x8+x9+x13+x14 |

| g7(x) | 1+x2+x5+x6+x7+x10+x11+x13+x14 |

| g8(x) | 1+x5+x8+x9+x10+x11+x14 |

| g9(x) | 1+x+x2+x3+x9+x10+x14 |

| g10(x) | 1+x3+x6+x9+x11+x12+x14 |

| g11(x) | 1+x4+x11+x12+x14 |

| g12(x) | 1+x+x2+x3+x5+x6+x7+x8+x10+x13+x14 |

Биты немодулированного кадра формируют биты сообщения M = (mKbch– 1, mKbch– 2, ..., m1, m0) для BCH кодирования, где mKbch– 1 — первый бит заголовка BBHEADER, m0 — последний бит BBFRAME кадра (или поля заполнения, при его наличии). BCH кодирование информационных битов M = (mKbch– 1, mKbch– 2, ..., m1, m0) в кодовое слово достигается следующим образом:

- умножение полинома сообщения m(x) = (mKbch– 1 xkbch– 1, mKbch– 2 xkbch– 2, ..., m1 x, m0) на x Nbch– Kbch;

- деление x Nbch– Kbch m(x) на порождающий полином g(x). Пусть d(x) = dNbch– Kbch– 1 x Nbch– Kbch– 1+ ... + d1 x + d0 будет остаток;

- Составление выходного кодового слова I, которое формирует информационное слово для LDPC кодирования, а именно:

I = (i0, i1,..., i Nbch– 1) = (mKbch– 1, mKbch– 2,..., m1, m0, dNbch– Kbch– 1, d Nbch– Kbch– 2,..., d1, d0)

Эквивалентный полином кодового слова равен c(x) = xNbch– Kbch m(x) + d(x).

6.1.2 Внутреннее кодирование (LDPC)

LDPC кодер обрабатывает выходные данные внешнего кодирования, I = (i0, i1,..., iKldpc– 1), как информационный блок размером Kldpc = Nbch, и осуществляет систематическое кодирование его в кодовое слово Λ размером Nldpc, где:

Λ = (λ0, λ1, λ2,...,λNldpc– 1) = (i0, i1,..., iKldpc– 1, p0, p1,..., pNldpc– Kldpc– 1).

Параметры LDPC кодирования (Nldpc, Kldpc)приведены в таблице 6.

6.1.2.1 Внутреннее кодирование для стандартного FECFRAME кадра

Задача кодера заключается в определении Nldpc– Kldpc битов четности (p0, p1,..., pNldpc– Kldpc– 1) для каждого блока из Kldpc информационных бит, (i0, i1,..., iKldpc). Данная процедура выглядит следующим образом:

- Инициализация p0 = p1 = p2 = pNldpc– Kldpc– 1 = 0

- Первый информационный бит, i0 суммируется с нарастающим итогом в адресах битов четности, указанных в первой строке таблиц A.1—A.6. Например, для скорости 2/3 (смотрите таблицу A.3), (все суммы в формате полей Галуа второго порядка):

p317 = p317 ⊕ i0

p2255 = p2255 ⊕ i0

p2324 = p2324 ⊕ i0

p2723 = p2723 ⊕ i0

p3538 = p3538 ⊕ i0

p3576 = p3576 ⊕ i0

p6194 = p6194 ⊕ i0p6700 = p6700 ⊕ i0

p9101 = p9101 ⊕ i0

p10057 = p10057 ⊕ i0

p12739 = p12739 ⊕ i0

p17407 = p17407 ⊕ i0

p21039 = p21039 ⊕ i0 - Для следующих 359 информационных битов, im, m = 1, 2, ..., 359, im суммируются с нарастающим итогом в адресах битов четности {x + m mod360×Qldpc}mod(Nldpc – Kldpc), где x — адрес накопителя бита четности, соответствующий первому биту i0, а Qldpc — константа, зависящая от скорости кодирования и указанная в таблице 8a. Продолжая пример, для скорости 2/3 Qldpc = 60. Таким образом, например, для информационного бита i1 выполняются следующие операции:

p377 = p377 ⊕ i1

p2315 = p2315 ⊕ i1

p2384 = p2384 ⊕ i1

p2783 = p2783 ⊕ i1

p3598 = p3598 ⊕ i1

p3636 = p3636 ⊕ i1

p6254 = p6254 ⊕ i1p6760 = p6760 ⊕ i1

p9161 = p9161 ⊕ i1

p10117 = p10117 ⊕ i1

p12799 = p12799 ⊕ i1

p17467 = p17467 ⊕ i1

p21099 = p21099 ⊕ i1 - Для 361-го информационного бита i360, адреса накопителей битов четности приведены во второй строке таблиц A.1–A.6. Подобным образом адреса накопителей битов четности для следующих 359 информационных битов im, m = 361, 362, ..., 719, рассчитываются по формуле {x + (m mod360)×Qldpc}mod(Nldpc – Kldpc), где x — адрес накопителя бита четности, соответствующий первому биту i360, то есть данные во второй строке таблиц A.1–A.6.

- Аналогичным образом для каждой группы из 360 информационных битов, чтобы найти адреса накопителей битов четности, используется новая строка таблиц A.1–A.6.

После обработки всех информационных битов окончательные биты четности получаются следующим образом:

- Последовательно осуществляются следующие операции, начиная с i = 1

pi = pi ⊕ pi – 1, где i = 1, 2, ..., Nldpc – Kldpc – 1

- Окончательное содержимое pi, i = 0, 1, ..., Nldpc – Kldpc – 1, равно биту четности pi.

| Скорость кодирования | Qldpc |

|---|---|

| 1/2 | 90 |

| 3/5 | 72 |

| 2/3 | 60 |

| 3/4 | 45 |

| 4/5 | 36 |

| 5/6 | 30 |

6.1.2.2 Внутреннее кодирование для короткого FECFRAME кадра

Kldpc битов, кодированных кодом BCH, для формирования Nldpc битов должны быть подвергнуты систематическому кодированию, описанному в разделе 6.1.2.1 с заменой таблицы 8a на таблицу 8b, а таблиц приложения A на таблицы приложения B.

| Скорость кодирования | Qldpc |

|---|---|

| 1/4 | 36 |

| 1/3 | 30 |

| 2/5 | 27 |

| 1/2 | 25 |

| 3/5 | 18 |

| 2/3 | 15 |

| 3/4 | 12 |

| 4/5 | 10 |

| 5/6 | 8 |

6.1.3 Битовый перемежитель (для 16-QAM, 64-QAM и 256-QAM)

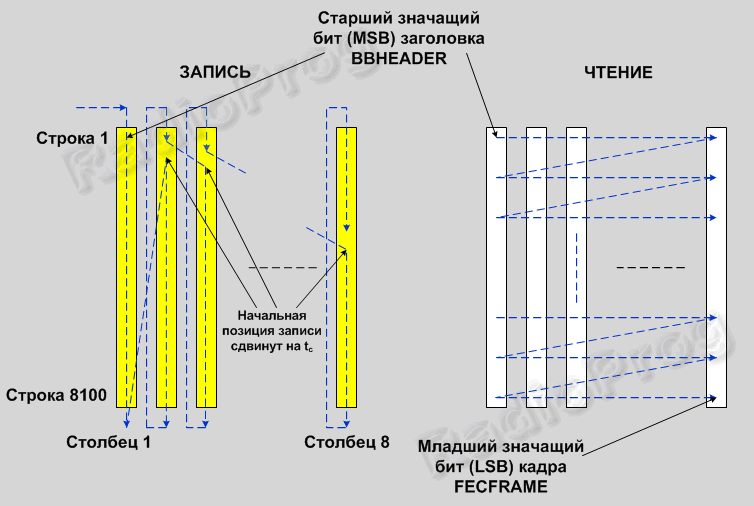

Выходные данные Λ LDPC кодера должны быть подвергнуты битовому перемежению, которое состоит из перемежения битов четности с последующей процедурой перемежения с закручиванием столбцов. Выходные данные перемежителя битов четности обозначаются U, а выходные данные перемежителя с закручиванием столбцов — V.

В перемежителе битов четности перемежение битов четности происходит согласно формулам:

- ui = λi для 0 ≤ i < Kldpc (информационные биты не перемежаются)

- uKldpc + 360t + s = λKldpc + Qldpc · s + t для 0 ≤ s < 360, 0 ≤ t < Qldpc

где Qldpc указана в таблицах 8a и 8b.

Для T2-Lite, при модуляции QPSK только со скоростями кодирования 1/3 и 2/5 применяется только перемежение битов четности (смотрите приложение I).

Конфигурация перемежения с закручиванием столбцов для каждого формата модуляции указана в таблице 9.

| Модуляция | Строки Nr | Столбцы Nc | |

|---|---|---|---|

| Nldpc = 64 800 | Nldpc = 16 200 | ||

| 16-QAM | 8 100 | 2 025 | 8 |

| 64-QAM | 5 400 | 1 350 | 12 |

| 256-QAM | 4 050 | — | 16 |

| — | 2 025 | 8 | |

В блоке перемежения с закручиванием столбцов биты данных ui из перемежителя битов четности поочередно постолбцово записываются в перемежитель с закручиванием столбцов и поочередно построчно считываются из него (MSB заголовка BBHEADER считывается первым) как показано на рисунке 13, где начальная позиция записи в каждом столбце сдвинута на tc в соответствии с таблицей 10. Данный перемежитель описывается следующим:

- Входной бит ui с индексом i, где 0 ≤ i < Nldpc, записывается в столбец ci, строку ri перемежителя, где

- ci = i divNr

- ri = (i + tci) modNr

- Выходной бит vj с индексом 0 ≤ j < Nldpc считывается из строки rj, столбца cj, где

- rj = j divNc

- cj = j modNc

Таким образом, для 64-QAM и Nldpc = 64 800 порядок выходных битов перемежителя с закручиванием столбцов будет выглядеть следующим образом:

(v0, v1, v2,..., v64799) = (u0, u5400, u16198,..., u53992, u59231, u64790)

Более полный список индексов на правой стороне, демонстрирующий все 12 столбцов: 0, 5 400, 16 198, 21 598, 26 997, 32 396, 37 796, 43 195, 48 595, 53 993, 59 392, 64 791, …… 5 399, 10 799, 16 197, 21 597, 26 996, 32 395, 37 795, 43 194, 48 594, 53 992, 59 391, 64 790.

| Модуляция | Столбцы Nc | Nldpc | Параметр закручивания tc | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Столбец 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | |||

| 16-QAM | 8 | 64 800 | 0 | 0 | 2 | 4 | 4 | 5 | 7 | 7 | — | — | — | — | — | — | — | — |

| 16 200 | 0 | 0 | 0 | 1 | 7 | 20 | 20 | 21 | — | — | — | — | — | — | — | — | ||

| 64-QAM | 12 | 64 800 | 0 | 0 | 2 | 2 | 3 | 4 | 4 | 5 | 5 | 7 | 8 | 9 | — | — | — | — |

| 16 200 | 0 | 0 | 0 | 2 | 2 | 2 | 3 | 3 | 3 | 6 | 7 | 7 | — | — | — | — | ||

| 256-QAM | 16 | 64 800 | 0 | 2 | 2 | 2 | 2 | 3 | 7 | 15 | 16 | 20 | 22 | 22 | 27 | 27 | 28 | 32 |

| 8 | 16 200 | 0 | 0 | 0 | 1 | 7 | 20 | 20 | 21 | — | — | — | — | — | — | — | — | |